jmpl

Assembly Syntax

jmpl address, regrd

op3

111000

Operation

Causes register-indirect delayed control transfer to the address given by [regrs1+ reg_or_immed] ????; The address of the jmpl instruction (the current contents of the PC) is copied into reg<rd

Comments

If either of the low-order two bits in the address is non-zero, mem_address_not_aligned exception occurs.

Example

jmpl subroutine_1, %r10

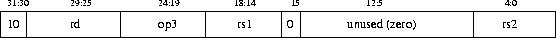

Instruction format

Instruction format

![]()

![]()