udivcc

Assembly Syntax

udivcc regrs1, reg_or_imm, regrd

op3

011110

Operation

Signed division. Concatenates %y register with low 32 bits of regrs1, performs division and writes result as 32-bit number into regrd; %y register is undefined afterwards.

Comments

Sets the condition codes. Division is an expensive operation; when possible, it should be avoided (see shift instructions)

Example

udivcc %r1, %r2, %r3

Example

udivcc %r1, 2, %r1

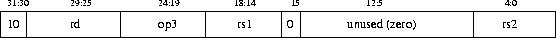

Instruction format

Instruction format

![]()

![]()