smul

Assembly Syntax

smul regrs1, reg_or_imm, regrd

op3

001011

Operation

Signed multiply regrs1 with reg_or_imm and places the 32 most significant bits of the result in %y and the rest in regrd.

Comments

none

Example

smul %r1, %r2, %r3

Example

smul %r1, -2, %r3

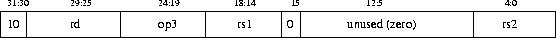

Instruction format

Instruction format

![]()

![]()